CPU Spec / Feature

CPU仕様・特長

AMD EPYC™ 7003シリーズプロセッサー

特長

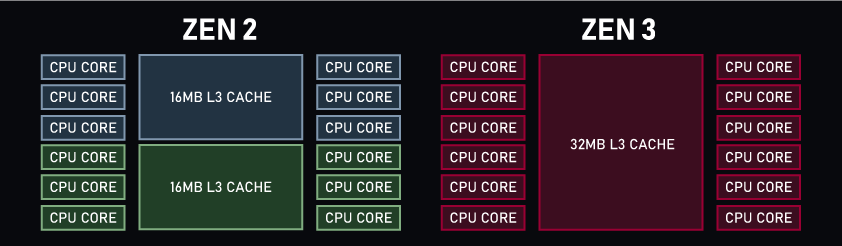

AMD EPYC™の第3世代にあたるAMD EPYC™ 7003シリーズプロセッサー(開発コード名:Milan)は、Zen 3マイクロアーキテクチャーを採用したCPUです。Zen 3マイクロアーキテクチャーは、前世代のZen 2マイクロアーキテクチャーの7nm製造プロセスにさらに改良を加えた製造プロセスで製造され、同一クロックのAMD EPYC™ 7002シリーズプロセッサー(開発コード名:Rome)と比べて、コア単位でIPC(Instruction per cycle;1サイクル当たりの実行命令数)が+15%向上しています。また、L3キャッシュダイの構成が変わり、8コアで共有する32MB L3のキャッシュダイになっており、これにより1コアで32MB L3キャッシュを占有できるSKUバリエーションが可能になりました。

メモリはDDR-3200を支える実動1600MHzバス動作へ変わっています。AMD EPYC™ 7002シリーズプロセッサーでは内部バスクロックが最大1499MHzだったため、DDR4-3200メモリモジュール搭載時に同期できるまでにレイテンシがありました。Zen3マイクロアーキテクチャーではそのレイテンシが短縮され、これによりメモリへのランダムアクセス性能が向上しています。これはDeep Learning等の大量の画像を解析するときなどにも功を奏すると考えられます。

仕様一覧

AMD EPYC™ 7003シリーズ

| モデル | コア数 | 動作周波数 | Max. Boost Freq. (GHz) | L3 Cache (MB) | メモリ チャンネル 数 | 最大 DDR 周波数 (1DPC) | TDP (W) | 1ソケットの 理論メモリ帯域 (GB/s) | PCIe 4 Lanes | 2P/1P | 1CPU 倍精度 理論性能 (GFLOPS) |

|---|---|---|---|---|---|---|---|---|---|---|---|

| 7773X | 64 | 2.2 | 3.5 | 768 | 8 | 3200 | 280 | 204.8 | 128 | 2P/1P | 2252.8 |

| 7763 | 64 | 2.45 | 3.5 | 256 | 8 | 3200 | 280 | 204.8 | 128 | 2P/1P | 2508.8 |

| 7713 | 64 | 2 | 3.675 | 256 | 8 | 3200 | 225 | 204.8 | 128 | 2P/1P | 2048 |

| 7713P | 64 | 2 | 3.675 | 256 | 8 | 3200 | 225 | 204.8 | 128 | 1Ponly | 2048 |

| 7663 | 56 | 2 | 3.5 | 256 | 8 | 3200 | 240 | 204.8 | 128 | 2P/1P | 1792 |

| 7643 | 48 | 2.3 | 3.6 | 256 | 8 | 3200 | 225 | 204.8 | 128 | 2P/1P | 1766.4 |

| 7573X | 32 | 2.8 | 3.6 | 768 | 8 | 3200 | 280 | 204.8 | 128 | 2P/1P | 1433.6 |

| 75F3 | 32 | 2.95 | 4 | 256 | 8 | 3200 | 280 | 204.8 | 128 | 2P/1P | 1510.4 |

| 7543 | 32 | 2.8 | 3.7 | 256 | 8 | 3200 | 225 | 204.8 | 128 | 2P/1P | 1433.6 |

| 7543P | 32 | 2.8 | 3.7 | 256 | 8 | 3200 | 225 | 204.8 | 128 | 1Ponly | 1433.6 |

| 7513 | 32 | 2.6 | 3.65 | 128 | 8 | 3200 | 200 | 204.8 | 128 | 2P/1P | 1331.2 |

| 7473X | 24 | 2.8 | 3.7 | 768 | 8 | 3200 | 240 | 204.8 | 128 | 2P/1P | 1075.2 |

| 7453 | 28 | 2.75 | 3.45 | 64 | 8 | 3200 | 225 | 204.8 | 128 | 2P/1P | 1232 |

| 74F3 | 24 | 3.2 | 4 | 256 | 8 | 3200 | 240 | 204.8 | 128 | 2P/1P | 1228.8 |

| 7443 | 24 | 2.85 | 4 | 128 | 8 | 3200 | 200 | 204.8 | 128 | 2P/1P | 1094.4 |

| 7443P | 24 | 2.85 | 4 | 128 | 8 | 3200 | 200 | 204.8 | 128 | 1Ponly | 1094.4 |

| 7413 | 24 | 2.65 | 3.6 | 128 | 8 | 3200 | 180 | 204.8 | 128 | 2P/1P | 1017.6 |

| 7373X | 16 | 3.05 | 3.8 | 768 | 8 | 3200 | 240 | 204.8 | 128 | 2P/1P | 780.8 |

| 73F3 | 16 | 3.5 | 4 | 256 | 8 | 3200 | 240 | 204.8 | 128 | 2P/1P | 896 |

| 7343 | 16 | 3.2 | 3.9 | 128 | 8 | 3200 | 190 | 204.8 | 128 | 2P/1P | 819.2 |

| 7313 | 16 | 3 | 3.7 | 128 | 8 | 3200 | 155 | 204.8 | 128 | 2P/1P | 768 |

| 7313P | 16 | 3 | 3.7 | 128 | 8 | 3200 | 155 | 204.8 | 128 | 1Ponly | 768 |

| 72F3 | 8 | 3.7 | 4.1 | 256 | 8 | 3200 | 180 | 204.8 | 128 | 2P/1P | 473.6 |

※ 定格動作周波数とAVX時動作周波数を同一と仮定した場合の理論ピーク性能(計算式は、定格動作周波数×コア数×16)。

Contact

お問い合わせ

お客様に最適な製品をご提案いたします。まずは気軽にお問い合わせ下さい。

03-5446-5531

平日9:30~17:30 (土曜日、日曜日、祝祭日、年末年始、夏期休暇は、休日とさせていただきます。)